# **Space Heritage**

Space Research Center, Polish Academy of Sciences Bartycka 18a, 00-716 Warsaw, Poland http://labfpga.cbk.waw.pl/index\_en.html doc.: SRC\_FPGA\_TN01 date: July 2010

issue: 5

by: Piotr Orleański

<u>The group</u>: Piotr Orleański (Ph.D., group leader), Waldek Bujwan (M.Sc.), Andrzej Cichocki (Ph.D. student), Rafał Graczyk (Ph.D. student), Paweł Grudziński (M.Sc. student), Małgosia Michalska (M.Sc.), Michał Mosdorf (Ph.D. student), Witek Nowosielski (M.Sc.), Piotr Sitek (Ph.D. student), Konrad Skup (Ph.D. student), Marcin Stolarski (Ph.D.), Roman Wawrzaszek (Ph.D.), Tomek Zawistowski (Ph.D. student), Bożena Zwierzyńska, Wiesława Winek (technicians), plus a few students and engineers (mechanics, optics, electronics) occasionally incorporated to our team on demand.

The group has 30 years experience in space instrumentation, mostly in design of DCDC Converters, different control systems (microcontrollers

and FPGA) and House-Keeping electronics, most of them manufactured according to ESA or CNES requirements.

The group started in 80's from the design of the **family of spectrometers** (visible & NIR) to be used in ground (mostly agriculture and environmental) experiments.

Our first, complete satellite instrument was the CID TV camera for ISTOK1/PRIRODA project

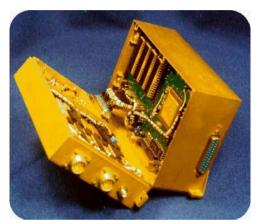

Figure -2 DCDC Converter for PFS MEX

on MIR Station. Camera (Figure -1) was controlled by 8-bit microprocessor, TV frames were processed on-board in order to control the pointing of ISTOK1 system towards the Sun. The camera was launched onboard PRIRODA Module in 1996.

In 1996 two "our" instruments were integrated on-board **Mars96** satellite and unsuccessfully launched to Mars: LPCE/CNRS in Orleans coordinated one of the lost instruments (**ELISMA**). Our contribution to this instrument

Figure -1 Engineering models of CID TV Camera (small, blue tube at the top plus black unit on the left) together with ISTOK1 IR Spectrometer, two big tubes at the bottom)

was the complete 20 Watts DCDC Converter, which supplied five different plasma waves analyzers and delivered about 20 galvanically separated rails to the users. ELISMA was manufactured according to CNES requirements for manufacturing of the space instrumentation.

The second instrument was the **Planetary Fourier Spectrometer** – the IR spectrometer coordinated by IFSI/CNR, Frascati and IKI/Moscow. SRC group was responsible of DCDC converter and EGSE equipment.

# **Space Heritage**

Space Research Center, Polish Academy of Sciences Bartycka 18a, 00-716 Warsaw, Poland http://labfpga.cbk.waw.pl/index\_en.html doc.: SRC\_FPGA\_TN01

date: July 2010 issue: 5

by: Piotr Orleański

Planetary Fourier Spectrometer was then selected by ESA for **Mars Express** and next to **Venus Express Missions**. IFSI/CNR coordinated the experiments, the technical activities were done mostly in Italy, however the Polish contribution was significantly increased. The group has delivered the DCDC Converter (Figure -2), the PFS Scanning System and partially EGSE. The previous, Mars 96 construction was refurbished according to ESA MEX requirements. Since January 2004 PFS perfectly works on Martian orbit.

Figure -3 Prototype of LFA for CESAR

In frame of Central Europe Initiative and program CESAR the group manufactured the prototypes of two complete space instruments - the Low Frequency Analyzer (Figure -3) for plasma investigations and IR **Fourier Spectrometer** for atmospheric studies. Both instruments were based on DSP techniques. The program was stopped before the entering the phase C/D. Only the prototypes have been manufactured and tested.

Another IR Fourier Spectrometer,

manufactured by our group in 1999, is still in use in the Remote Sensing Laboratory for on-ground studies on Earth atmosphere.

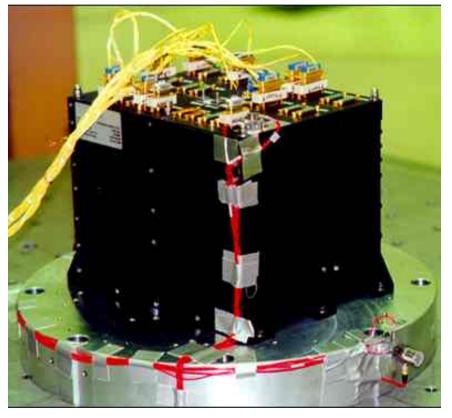

In 2002, as the part of the **Integral Mission, IBIS Gamma Ray Telescope** coordinated by IAS/CNR, Rome was launched. Within this project the group collaborated with Laben/Milano and University of Bergen and delivered complete **Veto System** for telescope. Our group manufactured the supply and control unit (Veto Electronics Box, VEB) for the anticoincidence system. The fully redundant, 8kg instrument fulfills ESA requirements for

Figure -4 VEB QM during the tests in ESTEC

# **Space Heritage**

Space Research Center, Polish Academy of Sciences Bartycka 18a, 00-716 Warsaw, Poland http://labfpga.cbk.waw.pl/index\_en.html doc.: SRC\_FPGA\_TN01 date: July 2010

issue: 5

by: Piotr Orleański

space instrumentation and contains of set of DCDC Converters (45 Watts), simple microcontroller block (80C32) and complex House-Keeping electronics including one channel spectrum analyzer. Since the launch in 2002 VEB (Figure -4) works properly on the orbit.

In mid of 2004 the small CNES satellite **DEMETER** was launched. The whole set of **Plasma Wave Instruments** coordinated by LPCE/CNRS was supplied by the DCDC Converter Block delivered by our group. The approach used for design DEMETER's DCDC was different than for the other projects SRC participated in. The goal was to deliver the set of standard (+5V, +/-12V, +/-15V, ...) secondary rails. Due to this, instead of using the SRC made, application oriented DCDC, the military graded commercial converters were used. The converters were qualified by CNES and equipped in SRC by EMC filters and control and House-Keeping electronics. Since June 2004 DCDC (Figure -6) works properly on the orbit.

Figure -5 HIFI Local Oscillator Control Unit

The next example of complete system designed in our group and dedicated for supplying, controlling and monitoring the complex instrument is the HIFI Local Oscillator Control Unit. In frame of ESA Herschel Project HIFI (Heterodyne Instrument for Far Infrared, SRON, Groningen), our group collaborates inside consortium of Max Planck Institute of Radioastronomy in Bonn, SRC Warsaw, JPL, Canadian Space Agency and COM DEV in Toronto. The consortium manufactures the programmable microwave source (Local Oscillator) working up to 2000GHz. Our group is

Figure -6 DEMETER's DCDC Converter

responsible of delivering about 100 Watts secondary power spread among of more than 120 different, floating and programmable (in most of the cases) rails. The rails supply the 30 GHZ synthesizer, microwave amplifiers and bias the microwave multipliers in 14 frequency bands (chains). The Microcontroller, 32KBytes of RAM, 16 Kbytes of PROM and RTX54SX32S FPGA from Actel are used in digital block. The software implemented in our unit, written in Assembler, controls the safety operations of the whole Local Oscillator Subsystem and, by this, fulfills one of the most critical and difficult tasks in HIFI. In addition more than 150 analogue channels are monitored by our system with 12 bits resolution, some of them are used

## **Space Heritage**

Space Research Center, Polish Academy of Sciences Bartycka 18a, 00-716 Warsaw, Poland http://labfoga.cbk.waw.pl/index\_en.html doc.: SRC\_FPGA\_TN01 date: July 2010

issue: 5

by: Piotr Orleański

internally in Local Oscillator for self checking, the others are distributed to Herschel telemetry system. The 16kg, fully redundant unit, is designed according to ESA requirements. The qualification model of the unit (Figure -5) passed successfully the tests in 2005. The flight model has been delivered to SRON in Groningen in 2006. The unit which has been launched in May 2009, failed in August 2009. After the successful recovery action in autumn 2009 the unit is still working well on the orbit. The full performance of the HIFI instrument has not been lost.

Within Chandrayaan Mission (ESA/India project to Moon launched in 2008) our group collaborates with MPIfS in Lindau and University of Bergen in the design and manufacturing of the infrared spectrometer SIR2. The group is responsible for delivery of 10W Power Supply Unit (PSU, Figure -7) including the programmable source for thermoelectric cooler and small HouseKeeping system. Four models have been delivered to Lindau and Bergen. The Flight Model of SIR-2 instrument was delivered to Bangalore in 2008. The instrument worked on Moon

orbit since October 2008 up to the last moment in 2009 when the control of the satellite was lost by Bangalore team.

Figure -7 Flight model of SIR-2 PSU

## **Actual projects**

During the **Beppi-Colombo** payload evaluation process, in 2004, ESA has selected the **Mercury Thermal Infrared Spectrometer** (MER-TIS) as one of 11 different instruments chosen for the orbiter. MER-TIS consists of optical head, common electronics, scanner and two calibration sources. Most of the MER-TIS blocks will be manufactured in DLR in Berlin. SRC PAS is responsible for delivery of MER-TIS Scanning System. The delivery includes the mechanical and optical system of the scanner, the electrical drivers for motor(s) (group's responsibility) and the VHDL code for state machine to be implemented inside instrument's FPGA and to be used for controlling the scanner (group's responsibility). The first model (prototype) of scanning system and VHDL code have been delivered to Berlin in 2008

The group participates in ESA ISS Project **ASIM** (Atmospheric-Space Interaction Monitor) in MXGS Instrument (Miniature X-Ray and Gamma-Ray Sensor, University of Bergen, University of Valencia, SRC PAS). The prototype of Low and High Voltage Power Supply Unit (80W, 40 different rails) has been manufactured in 2008 in SRC and tested in Bergen with the prototype of MXGS Detector module. Phase C/D of ASIM should start Q4 2010. The autonomous state machine, based on Actel FPGA,

# **Space Heritage**

Space Research Center, Polish Academy of Sciences Bartycka 18a, 00-716 Warsaw, Poland http://labfpga.cbk.waw.pl/index\_en.html doc.: SRC\_FPGA\_TN01 date: July 2010

date: July 201

issue: 5

by: Piotr Orleański

is used for control all output rails in the Power Supply Unit, more than 140 important points in MXGS (voltages, currents and temperatures) are monitored by this state machine also.

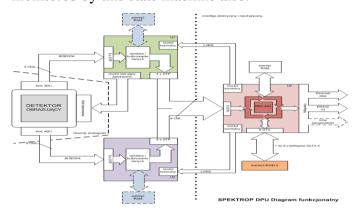

Figure -8 Block scheme of SPEKTROP digital part

Figure -9 The mock-up of BRITE

**Taranis Mission**, the continuation of CNES small satellite program, is the next project the group is involved in. MPU, the supply system proposed by SRC group and dedicated for whole Taranis payload is the part of **MEXIC Unit** (LPCEE-Orleans). MPU is based on the set of DCDCC converters from STEEL equipped with the FPGA based Control and HouseKeeping system (state machine similar to that one proposed for ASIM).

**"FPGA based high power DCDC Converters"** is the research contract signed in 2009 with EADS Astrium. The project focuses on digital (implemented inside FPGA) feed-back loop for the satellite high power DCDC converter.

In 2009 Polish Ministry of Sciences and High Educations initiated two R&D contracts for:

- SPEKTROP the airborne/space IR and visible imaging systems the activities in the laboratory focus on FPGA based electronics for CCD and CMOS arrays, FPGA based real time image processing, FPGA based main processing unit, Figure -8,

- FPGA based, re-programmable processing units for space applications where the combination of reliable antifuse Actel RadHard chip and reprogramable but SEU sensitive SRAM-based Xilnix chip is applied for potential space applications.

The contracts are still ongoing, the results are expected in 2011.

BRITE (constellation of two Canadian, two Austrian and two Polish small satellites) is the first Polish project where the whole satellite will be integrated and tested in Poland. The satellite is developed in Space Flight Laboratory, University of Toronto, most of the parts for the first BRITE-PL satellite will be manufactured in Canada and delivered as subsystems to SRC. For the second BRITE-PL satellite the involvement of SRC engineers in developing and manufacturing phases will be significantly bigger. The satellites will observe the long-term changes of brightness of the stars (brighter than 3.5mag). Satellite's payload consists of small telescope with 10M pixels CCD. Satellite is 20x20x20 cm big,

# **Space Heritage**

Space Research Center, Polish Academy of Sciences Bartycka 18a, 00-716 Warsaw, Poland http://labfpga.cbk.waw.pl/index\_en.html doc.: SRC\_FPGA\_TN01 date: July 2010

issue: 5

by: Piotr Orleański

weight about 7 kg and is equipped by a unique ACS system (Sun Sensors, Magnetometer, Star Tracker, Magnetotorquers and miniature Reaction Wheels). Whole staff of the Laboratory is highly involved in the project (power, communication, on-board software, all computers, electronics of the telescope). The launches of Austrian satellites are scheduled for mid 2011. The first Polish and both Canadian satellites are planned to be launched in 20111/12. The BRITE technical activities in Poland should be finished in 2013 when the second Polish satellite is planned to be launched.

**RecAv** project is actually starting as the R&D contract supported by EADS Astrium. The goal of the project is to research on dynamically reconfigurable hardware for improvement of reliability, availability and multiplexing functionality of aerospace avionics and on board computing.

## **Future planned projects**

- For **Solar Orbiter Mission** the Laboratory will be responsible for IDPU (Atmel RTC plus additional FPGA dedicated for detector's data acquisition plus big mass memory) for **STIX Spectrometer**. The participation of the group in instrument's consortiums is already agreed, STIX is already included to SO Payload, the Mission has still to be approved by ESA.

- **RAHDHIFFS** is the proposal accepted within FP7-SPACE-2010-1. The consortium led by Atmel (EADS, TAS, CNES, Surrey University, SRC and others) has proposed to start from the commercially available Abound Logic based FPGA revolutionary architecture, then to design and produce prototypes of a European space radiation hardened by design reprogrammable FPGA and to validate it at end user applications. The activities are planned to start at the end of 2010.

## **Facilities**

**The Laboratory** has been completely refurbished at the beginning of 2009 (*support from Foundation for Polish Science*). On 150m<sup>2</sup> of ESD Protected Area our employers can design, manufacture and tests the digital and analogue/digital blocks based on different types of FPGA's. DSP techniques can be implemented for the signals up to 1GHz. Laboratory shares the common SRC PAS facilities: 200m<sup>2</sup> clean room, TV chamber, two climatic chambers, simplified stands for EMC and vibration tests, mechanical workshop (two CNC machines).